Производство 14-слойных 3-ступенчатых печатных плат для тестирования полупроводников

Производство 14-слойных 3-ступенчатых печатных плат для тестирования полупроводников является одним из основных процессов в области тестирования полупроводниковых микросхем, обеспечивая высокопроизводительное аппаратное обеспечение для тестирования функций микросхем и проверки их надежности.

Описание

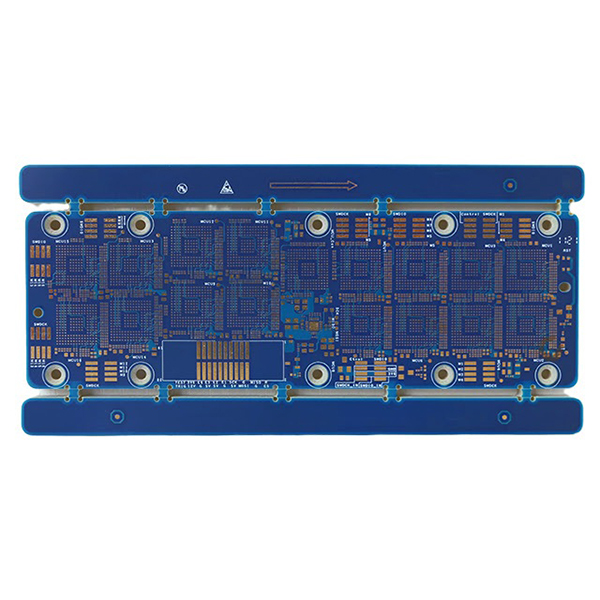

14-слойная, 3-ступенчатая печатная плата для тестирования полупроводников

14-слойная, 3-ступенчатая печатная плата для тестирования полупроводников, отличающаяся высокой плотностью, высокой точностью и высокой надежностью, широко используется в различных современных устройствах для тестирования полупроводников и служит ключевой основой для обеспечения качества и производительности микросхем.

Основные характеристики 14-слойной, 3-ступенчатой печатной платы для тестирования полупроводников

- Многослойное соединение высокой плотности:14-слойная структура в сочетании с 3-ступенчатой технологией HDI поддерживает сложные схемы и изоляцию нескольких сигналов, отвечая требованиям высокой плотности и высокоскоростной передачи сигналов.

- Точный производственный процесс:Используется высококачественный материал Shengyi S1000-2M с позолоченной поверхностью, минимальным диаметром отверстий 0,5 мм и минимальным расстоянием между дорожками/пространством 4/4 мил, подходящий для тестирования с мелким шагом и высокой точностью.

- Высокая надежность и целостность сигнала:Передовая технология погружных/слепых переходных отверстий и межслойных соединений значительно повышает целостность сигнала и противопомеховые характеристики, обеспечивая точность тестовых данных.

- Превосходные материалы и качество изготовления:Высокая термостойкость и коррозионная стойкость, подходит для длительных и сложных испытаний.

- Гибкий дизайн и возможность настройки:Поддержка различных тестовых интерфейсов и индивидуальных конструкций, что упрощает интеграцию в различные тестовые системы.

Введение в 14-слойную 3-ступенчатую плату для тестирования полупроводников

- 14 слоев:Относится к 14 проводящим слоям внутри печатной платы, что позволяет осуществлять сложные соединения цепей и изоляцию сигналов посредством многослойного наложения, подходит для требований высокой плотности и высокой скорости сигнала, а также способствует целостности сигнала и электромагнитной совместимости.

- 3 этапа:Обычно относится к «этапам» в технологии HDI (High Density Interconnect) — три процесса лазерного сверления и три процесса ламинирования, поддерживающие более тонкие погруженные/слепые структуры для более гибких соединений и более высокой плотности, подходящие для высокоскоростных/высокочастотных приложений.

- Тестовая плата для полупроводников:Специально используется для таких функций, как тестирование функций чипа и тестирование на старение, требующих высокой надежности, высокой точности и отличной способности передачи сигнала.

Основные области применения

- Системы тестирования полупроводников, такие как устройства для тестирования чипов, автоматическое тестовое оборудование ATE, пробные карты и нагрузочные платы.

- Тестовые сценарии с высокими требованиями, такие как тестирование функций ИС, тестирование на старение и анализ отказов.

- Подходит для упаковки и тестирования полупроводников, а также для научно-исследовательских и опытно-конструкторских работ, требующих высокой частоты, высокой скорости, высокой точности и высокой надежности.

English

English  Français

Français  Tiếng Việt

Tiếng Việt  Italiano

Italiano  Nederlands

Nederlands  Türkçe

Türkçe  Svenska

Svenska  Polski

Polski  Română

Română  Latviešu

Latviešu  한국어

한국어  Русский

Русский  Español

Español  Deutsch

Deutsch  Українська

Українська  Português

Português  العربية

العربية  Indonesian

Indonesian  Čeština

Čeština  Suomi

Suomi  Eesti

Eesti  Български

Български  Dansk

Dansk  Lietuvių

Lietuvių  Bokmål

Bokmål  Slovenčina

Slovenčina  Slovenščina

Slovenščina  Ελληνικά

Ελληνικά  Magyar

Magyar  עברית

עברית